TR2014-014

FPGA Implemented Multi-Level IFPWM Power Coding for Class-S PA in an All-Digital GHz LTE Transmitter

-

- , "FPGA Implemented Multi-Level IFPWM Power Coding for Class-S PA in an All-Digital GHz LTE Transmitter", IEEE International Wireless Symposium (IWS), March 2014.BibTeX TR2014-014 PDF

- @inproceedings{Zhu2014mar,

- author = {Zhu, Q. and Ma, R. and Duan, C. and Yamanaka, K. and Teo, K.H.},

- title = {{FPGA Implemented Multi-Level IFPWM Power Coding for Class-S PA in an All-Digital GHz LTE Transmitter}},

- booktitle = {IEEE International Wireless Symposium (IWS)},

- year = 2014,

- month = mar,

- url = {https://www.merl.com/publications/TR2014-014}

- }

- , "FPGA Implemented Multi-Level IFPWM Power Coding for Class-S PA in an All-Digital GHz LTE Transmitter", IEEE International Wireless Symposium (IWS), March 2014.

-

Research Areas:

Abstract:

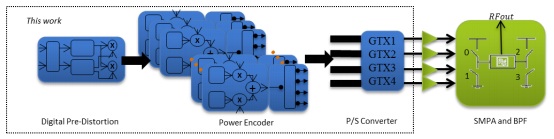

This work presents a new efficient multi-level intermediate frequency pulse width modulation (ML-IFPWM) power coding algorithm for switch-mode power amplifier. The merits of high power coding efficiency with distortion correction function are demonstrated by a FPGA implemented digital front end. Measurement results have shown power coding efficiency greater than 45%. To our knowledge, this is the firstly reported implemented discrete-time domain 3-level power encoding approach with 5-MHz LTE signal at RF carrier frequency around 2 GHz. This can be used to generate multi-level digital pulse-train for advanced class-S PA in cellular digital base stations.